Introduction to GeMRTOS system architecture #

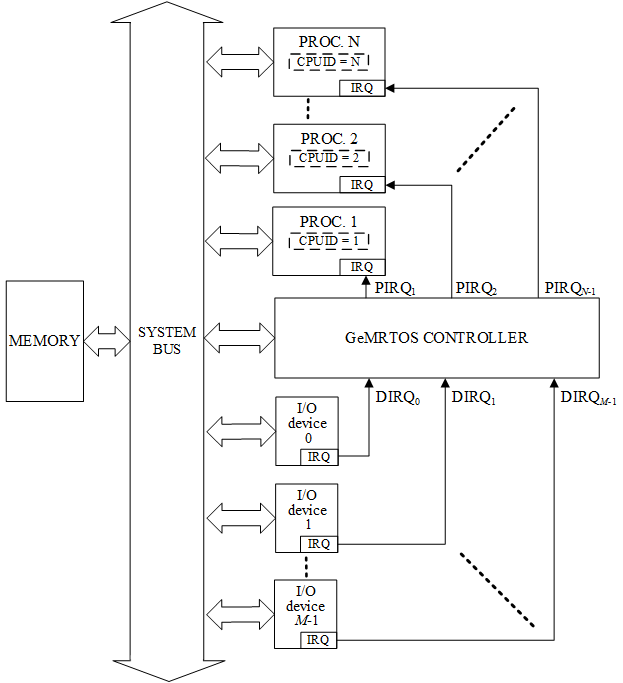

In the GeMRTOS system architecture, a set of N processors shares a common memory and M input/output devices through a common bus. FIG. 2 shows a layout of the GeMRTIOS controller interconnection in a multiprocessor architecture. The GeMRTOS controller receives device interrupt requests (DIRQs) from input/output peripheral devices. The GeMRTOS controller sends processor interrupt requests (PIRQs) to the system processors. The system bus allows the processors to share the system memory. Each processor has a unique internal identification register CPUID.

GeMRTOS with Intel Nios II processors #

(Nios is a trademark of Intel Corporation or its subsidiaries.)

The GeMRTOS multiprocessor system is implemented based on the Nios II processor of Intel Corporation. The system architecture is designed using the Platform Designer tool from Intel Corporation. GeMRTOS is implemented as a Platform Designer component that can be added naturaly to create multiprocessor systems.