GeMRTOS Multiprocessor IP component

The GeMRTOS Multiprocessor IP component simplifies the design of multiprocessor systems by reducing the complexity of processor booting, synchronization, and mutual exclusion, making it as straightforward to design a multiprocessor system as it is to design a uniprocessor system.

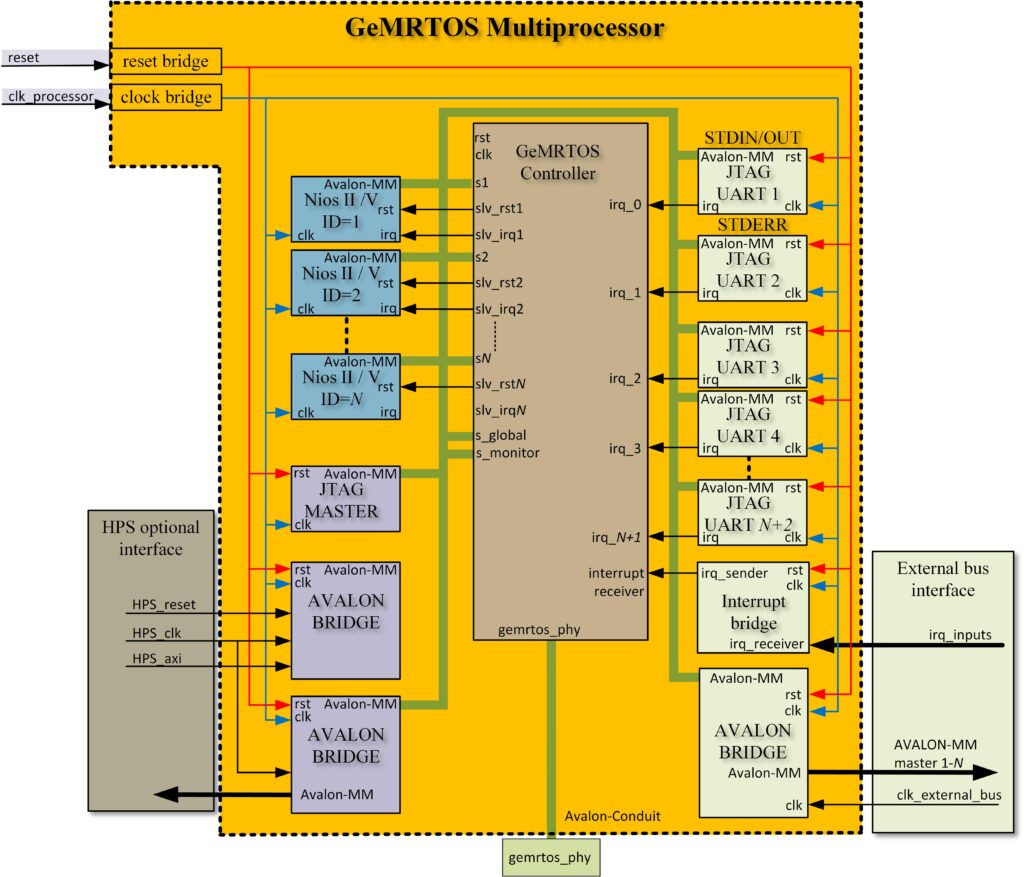

As shown in Figure 3, the structure of the GeMRTOS Multiprocessor IP includes the following components:

- The GeMRTOS controller: This serves as the core of the GeMRTOS Multiprocessor IP component, responsible for time management and external events, and enabling the gemrtos Avalon-conduit port for easy access to external signals.

- The System Processor: The IP component supports Nios II and Nios V soft-processors in various versions and parametrizations.

- The MM-Avalon bridge for external devices: This bridge allows for the definition of different clock sources for processors and external devices, thereby enabling clock domain adaptation to improve overall performance.

- The JTAG-UART devices: These devices can be enabled for STDIO and STDERR consoles, as well as for each system processor, which simplifies design and facilitates system debugging.

The MM-Avalon bridge for HPS interface: This allows access to and from the HPS domain memory map, though deep knowledge is required for effective use.

Overall, the GeMRTOS Multiprocessor IP component significantly reduces the challenges associated with designing complex multiprocessor systems, thereby streamlining the development process and improving efficiency.