System Architecture

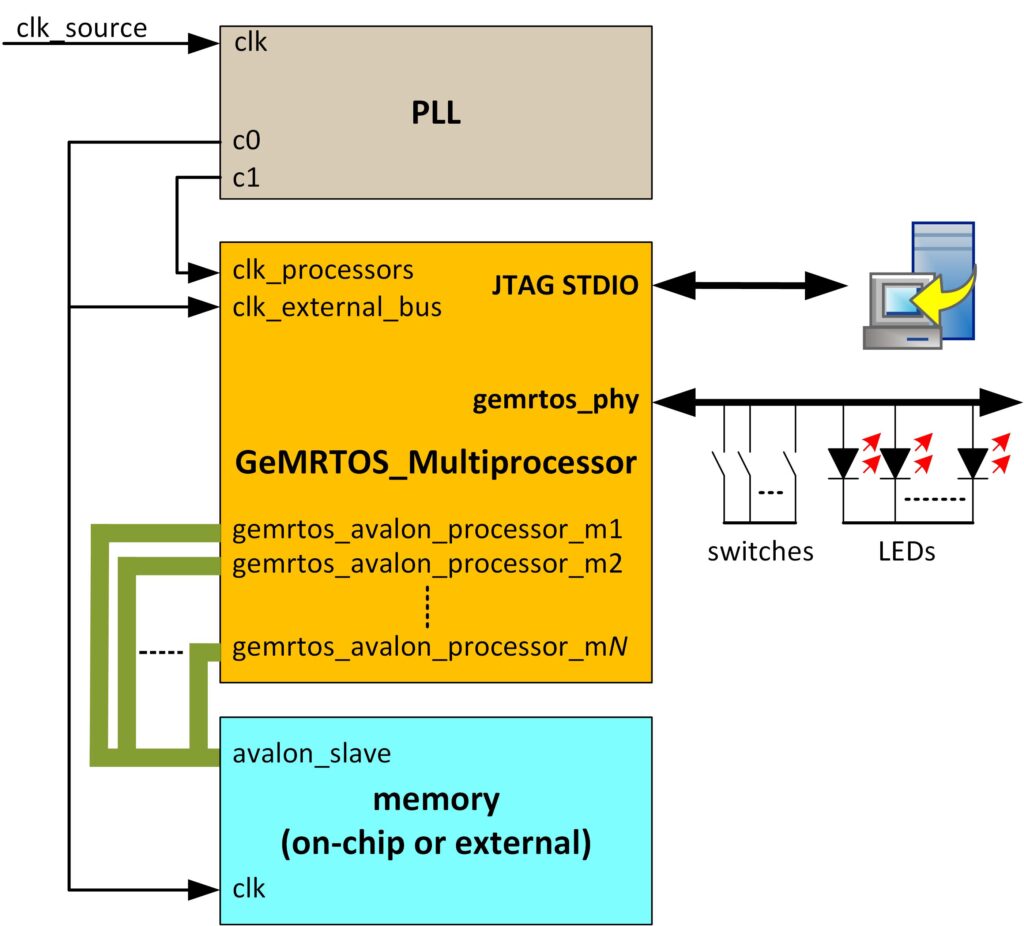

The proposed reference design is centered around the GeMRTOS Multiprocessor IP. The system is completed by adding the following components:

- PLL Component: GeMRTOS supports different clocks for processors and system devices. To enhance system performance, the processors are configured to run at 25 MHz, while the system bus clock is set to 100 MHz.

- Memory component or memory controller: The system includes memory to store applications.

The system architecture resembles that of a uniprocessor system based on the Nios II or Nios V soft-processor, with the GeMRTOS controller replacing the processor. Additionally, the architecture is simplified as it does not require a timer device or the JTAG UART typically found in Altera’s soft-processor examples.

The GeMRTOS multiprocessor IP component includes optional JTAG UARTs for STDIO and STDERR consoles, which the user may choose to enable through the parameter configuration GUI. It also provides a JTAG UART for each processor, which can be enabled and may be found useful for debugging purposes. Additionally, it features a conduit port for easy management of LEDs and switches on most development FPGA boards. The GeMRTOS multiprocessor IP component is designed to simplify the complex task of multiprocessor design.

Figure 1 demonstrates the proposed design architecture.

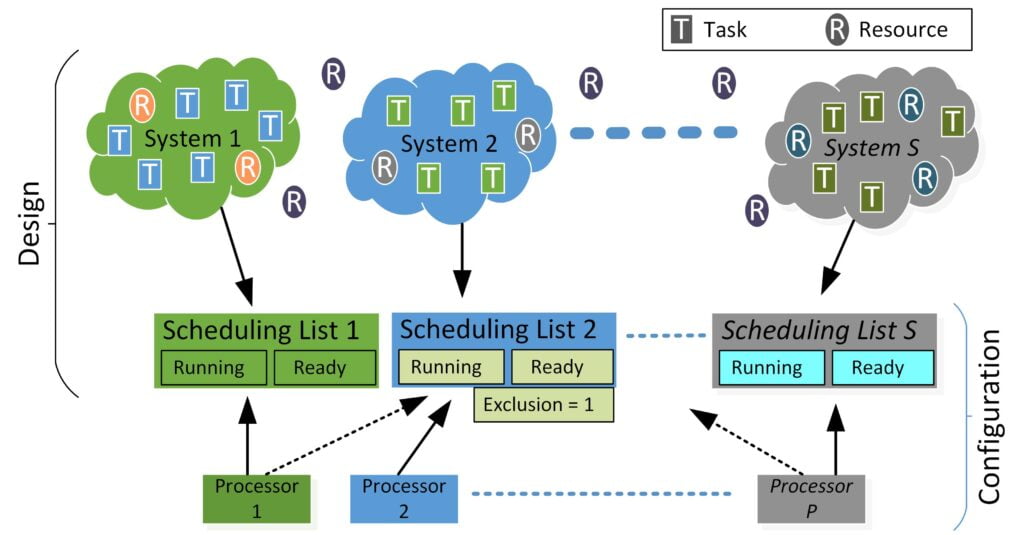

The software architecture of GeMRTOS allows applications to be configured as a set of tasks assigned to hybrid scheduling lists. GeMRTOS employs an innovative hybrid partitioned scheduling approach that leverages these lists to optimize task execution across multiple processors. Tasks are assigned to scheduling lists either statically or dynamically, and processors are allocated to one or more of these lists. This flexible configuration supports the partial implementation of partitioned/semi-global scheduling, ensuring that processors do not remain idle when tasks are available in their assigned scheduling lists. Figure 4 demonstrates how tasks and processors can be allocated using the GeMRTOS hybrid scheduling list.

Management of tasks, resources, and scheduling algorithms is easily implemented due to the flexible multiprocessor architecture of GeMRTOS.